www.DataSheet4U.com

# **CAT661**

# High Frequency 100mA CMOS Charge Pump, Inverter/Doubler

#### **FEATURES**

- Converts V+ to V- or V+ to 2V+

- Low output resistance, 10Ω max.

- High power efficiency

- Selectable charge pump frequency of 25kHz or 135kHz; optimize capacitor size.

- Low quiescent current

- Pin-compatible to MAX660, LTC660 with higher frequency operation

- Available in 8-pin SOIC andDIP packages

- Lead-free, halogen-free package option

#### **APPLICATIONS**

- Negative voltage generator

- **Voltage doubler**

- Voltage splitter

- Low EMI power source

- GaAs FET biasing

- Lithium battery power supply

- Instrumentation

- LCD contrast bias

- **■** Cellular phones, pagers

### **DESCRIPTION**

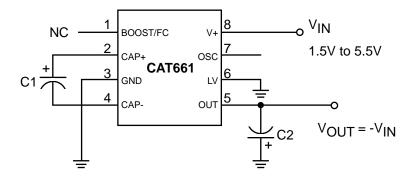

The CAT661 is a charge-pump voltage converter. It can invert a positive input voltage to a negative output. Only two external capacitors are needed. With a guaranteed 100mA output current capability, the CAT661 can replace a switching regulator and its inductor. Lower EMI is achieved due to the absence of an inductor.

In addition, the CAT661 can double a voltage supplied from a battery or power supply. Inputs from 2.5V to 5.5V will yield a doubled, 5V to 11V output.

A Frequency Control pin (BOOST/FC) is provided to select either a high (typically 135kHz) or low (25kHz) internal oscillator frequency, thus allowing quiescent current vs. capacitor size trade-offs to be made. The 135kHz frequency is selected when the FC pin is

connected to V+. The operating frequency can also be adjusted with an external capacitor at the OSC pin or by driving OSC with an external clock.

Both 8-pin DIP and SO packages are available. For die availability, contact Catalyst Semiconductor marketing.

The CAT661 can replace the MAX660 and the LTC660 in applications where higher oscillator frequency and smaller capacitors are needed. In addition, the CAT661 is pin compatible with the 7660/1044, offering an easy upgrade for applications with 100mA loads.

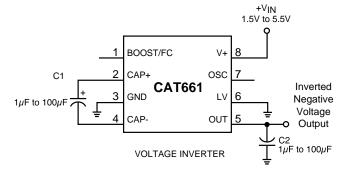

#### TYPICAL APPLICATION

# PIN CONFIGURATION

## **PIN DESCRIPTIONS**

|            |          | Circuit Configu                                                                                                                                                                                                                            |                                  |                                                                                                                                                               |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Number | Name     | Inverter                                                                                                                                                                                                                                   |                                  |                                                                                                                                                               |

| 1          | Boost/FC | Freqency Control for the internal oscillator. With an external oscillator BOOST/FC has no effect.                                                                                                                                          |                                  | Same as inverter.                                                                                                                                             |

|            |          | Boost/FC                                                                                                                                                                                                                                   | Oscillator Frequency             | <b>∪</b> scillator Frequency                                                                                                                                  |

|            | ľ        | Open                                                                                                                                                                                                                                       | 25kHz typical, 10kHz minimum     | 40kHz typical                                                                                                                                                 |

|            | ·        | V+                                                                                                                                                                                                                                         | 135kHz typical, 80kHz minimum    | 135kHz typical, 40kHz minimum                                                                                                                                 |

| 2          | CAP+     | Charge Pun                                                                                                                                                                                                                                 | np Capacitor. Positive terminal. | Same as inverter.                                                                                                                                             |

| 3          | GND      | Power Supp                                                                                                                                                                                                                                 | oly Ground.                      | Power supply. Positive voltage input.                                                                                                                         |

| 4          | CAP-     | Charge pum                                                                                                                                                                                                                                 | np capacitor. Negative terminal. | Same as inverter.                                                                                                                                             |

| 5          | OUT      | Output for negative voltage.                                                                                                                                                                                                               |                                  | Power supply ground.                                                                                                                                          |

| 6          | LV       | Low-Voltage selection pin. When the input voltage is less than 3V, connect LV to GND. For input voltages above 3V, LV may be connected to GND or left open. If OSC is driven externally, connect LV to GND.                                |                                  | LV must be tied to OUT for all input voltages.                                                                                                                |

| 7          | osc      | Oscillator control input. An external capacitor can be connected to lower the oscillator frequency. An external oscillator can drive OSC and set the chip operating frequency. The charge-pump frequency is one-half the frequency at OSC. |                                  | Same as inverter. Do not overdrive OSC in doubling mode. Standard logic levels will not be suitable. See the applications section for additional information. |

| 8          | V+       | Power supp                                                                                                                                                                                                                                 | ly. Positive voltage input.      | Positive voltage output.                                                                                                                                      |

# **ORDERING INFORMATION**

| Part Number  | Package      | Quanity    | Package<br>Marking |

|--------------|--------------|------------|--------------------|

| CAT661ELA    | PDIP, 8-lead | 50/tube    | 661ELA             |

| CAT661EVA    | SOIC         | 100/tube   | 661EVA             |

| CAT661EVA-T3 | SOIC         | 3,000/reel | 661EVA             |

Note: All packages are RoHS compliant.

# WWW.DataShatall.come MAXIMUM RATINGS

| V+ to GND6V                                                                                   |          |

|-----------------------------------------------------------------------------------------------|----------|

|                                                                                               | Storag   |

| Input Voltage (Pins 1, 6 and 7)0.3V to (V+ + 0.3V)                                            | Lead S   |

|                                                                                               | ESD F    |

| BOOST/FC and OSC Input Voltage The least negative of (Out - 0.3V) or (V+ - 6V) to (V+ + 0.3V) | Note: T  |

| Output Short-circuit Duration to GND 1 sec.                                                   | These a  |

| (OUT may be shorted to GND for 1 sec without damage but                                       | time per |

| shorting OUT to V+ should be avoided.)                                                        | respect  |

| Continuous Power Dissipation (T <sub>A</sub> = 70°C)                                          | C        |

| Plastic DIP730mW                                                                              | C        |

| SO500mW                                                                                       |          |

| TDFN 1W                                                                                       |          |

| Storage Temperature65°C to          | 160°C |

|-------------------------------------|-------|

| Lead Soldering Temperature (10 sec) | 300°C |

| ESD Rating-Human Body Model         | 2000V |

|                                     |       |

Note:  $T_A$  = Ambient Temperature

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolongued time periods may affect device reliability. All voltages are with respect to ground.

### **Operating Ambient Temperature Ranges**

CAT661E ..... -40°C to 85°C

## **ELECTRICAL CHARACTERISTICS**

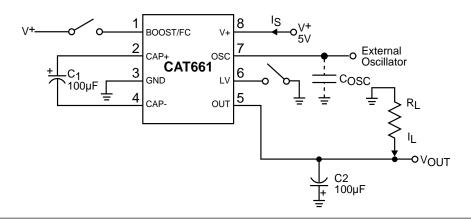

V+ = 5V, C1 = C2 =  $100\mu$ F, Boost/FC = Open, C<sub>OSC</sub> = 0pF, and Test Circuit is Figure 1 unless otherwise noted. Temperature is  $T_A = T_{AMIN}$  to  $T_{AMAX}$  unless otherwise noted.

| Parameter            | Symbol | Conditions                                      | Min. | Тур  | Max. | Units |

|----------------------|--------|-------------------------------------------------|------|------|------|-------|

|                      |        | Inverter: LV = Open. $R_L = 1k\Omega$           | 3.0  |      | 5.5  | V     |

| Supply Voltage       | VS     | Inverter: LV = GND. $R_L = 1k\Omega$            | 1.5  |      | 5.5  |       |

|                      |        | Doubler: LV = OUT. $R_L = 1k\Omega$             | 2.5  |      | 5.5  |       |

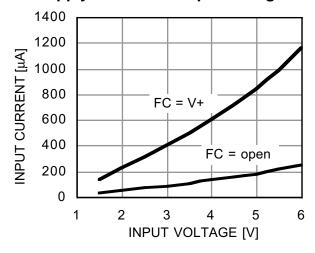

| Supply Current       | IS     | BOOST/FC = open, LV = Open                      |      | 0.2  | 0.5  | mA    |

|                      |        | BOOST/FC = V+ , LV = Open                       |      | 1    | 3    |       |

| Output Current       | IOUT   | OUT is more negative than -4V                   | 100  |      |      | mA    |

| Output Resistance    | RO     | $C1 = C2 = 10\mu F$ ,                           |      | 3.5  | 10   | Ω     |

|                      |        | BOOST/FC = V+ (C1, C2 ESR $\leq$ 0.5 $\Omega$ ) |      |      |      |       |

|                      |        | C1 = C2 = 100μF (Note 2)                        |      | 3.5  | 10   |       |

| Oscillator Frequency | FOSC   | BOOST/FC = Open                                 | 10   | 25   |      | kHz   |

| (Note 3)             |        | BOOST/FC = V+                                   | 80   | 135  |      |       |

| OSC Input Current    | IOSC   | BOOST/FC = Open                                 |      | ±2   |      | μΑ    |

|                      |        | BOOST/FC = V+                                   |      | ±10  |      |       |

| Power Efficiency     | PE     | $R_L = 1k\Omega$ connected between V+ and       | 96   | 98   |      | %     |

|                      |        | OUT, $T_A = 25^{\circ}C$ (Doubler)              |      |      |      |       |

|                      |        | $R_L = 500\Omega$ connected between GND and     | 92   | 96   |      |       |

|                      |        | OUT, $T_A = 25^{\circ}C$ (Inverter)             |      |      |      |       |

|                      |        | $I_L = 100$ mA to GND, $T_A = 25$ °C (Inverter) |      | 88   |      |       |

| Voltage Conversion   | VEFF   | No load, $T_A = 25^{\circ}C$                    | 99   | 99.9 |      | %     |

| Efficiency           |        |                                                 |      |      |      |       |

<sup>1.</sup> In Figure 1, test circuit electrolytic capacitors C1 and C2 are  $100\mu F$  and have  $0.2\Omega$  maximum ESR. Higher ESR levels may reduce efficiency and output voltage.

<sup>2.</sup> The output resistance is a combination of the internal switch resistance and the external capacitor ESR. For maximum voltage and efficiency keep external capacitor ESR under  $0.2\Omega$ .

<sup>3.</sup> FOSC is tested with  $C_{OSC}$  = 100pF to minimize test fixture loading. The test is correlated back to  $C_{OSC}$ =0pF to simulate the capacitance at OSC when the device is inserted into a test socket without an external  $C_{OSC}$ .

ww.FataSheet4Ucom Figure 1. Test Circuit Voltage Inverter

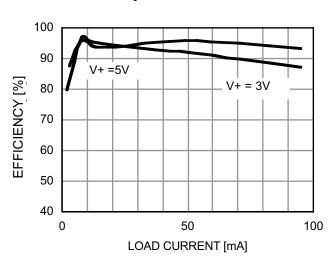

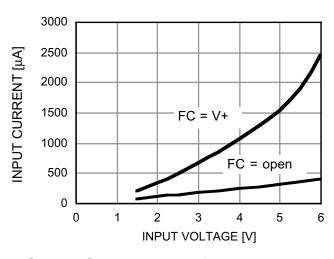

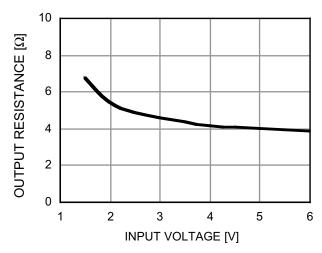

#### TYPICAL OPERATING CHARACTERISTICS

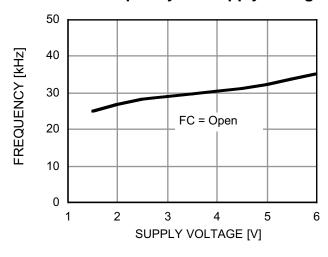

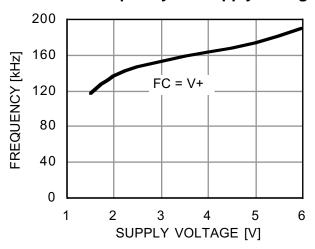

Typical characteristic curves are generated using the circuit in Figure 1. Inverter test conditions are: V+5V, LV=GND, BOOST/FC=Open and  $T_A=25^{\circ}C$  unless otherwise indicated. Note that the charge-pump frequency is one-half the oscillator frequency.

## Supply Current vs. Input Voltage

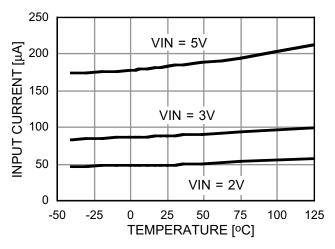

# **Supply Current vs. Temperature (No Load)**

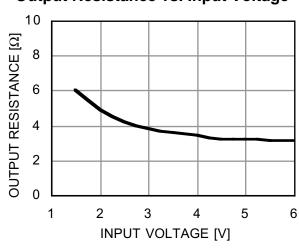

## **Output Resistance vs. Input Voltage**

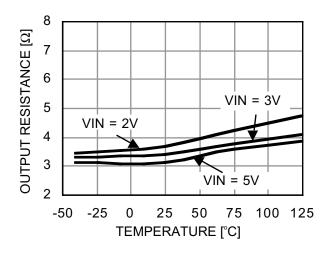

# Output Resistance vs. Temperature (50 $\Omega$ load)

# WWW.DataShart OPERATING CHARACTERISTICS

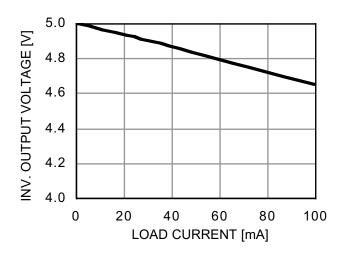

# Inverted Output voltage vs. Load, V+ = 5V

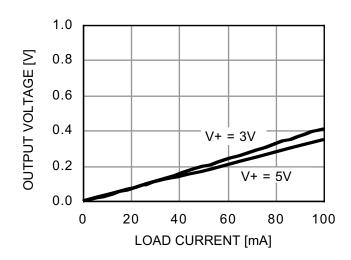

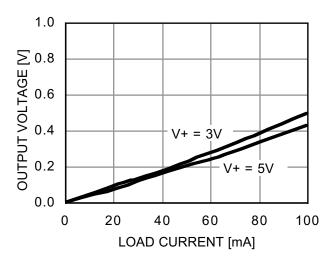

## **Output Voltage Drop vs. Load Current**

# Oscillator Frequency vs. Supply Voltage

Oscillator Frequency vs. Supply Voltage

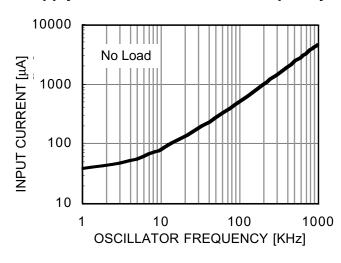

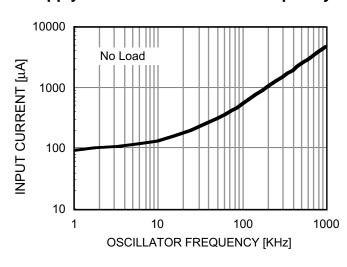

# **Supply Current vs. Oscillator Frequency**

# **Efficiency vs. Load Current**

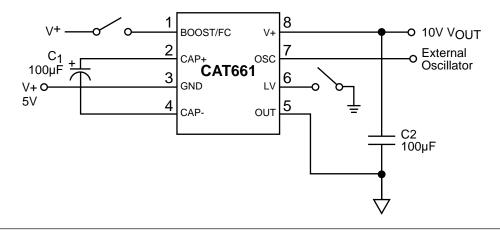

Figure 2. Test Circuit Voltage Doubler

### TYPICAL OPERATING CHARACTERISTICS

Typical characteristic curves are generated using the circuit in Figure 2. Doubler test conditions are: V+5V, LV=GND, BOOST/FC=Open and  $T_A=25^{\circ}C$  unless otherwise indicated.

# **Supply Current vs. Input Voltage (No Load)**

# Output Resistance vs. Input Voltage

## **Supply Current vs. Oscillator Frequency**

## **Output Voltage Drop vs. Load Current**

# WWW.DataSheet4U.comTION INFORMATION

#### **Circuit Description and Operating Theory**

The CAT661 switches capacitors to invert or double an input voltage.

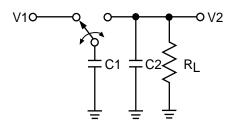

Figure 3 shows a simple switch capacitor circuit. In position 1 capacitor C1 is charged to voltage V1. The total charge on C1 is Q1 = C1V1. When the switch moves to position 2, the input capacitor C1 is discharged to voltage V2. After discharge, the charge on C1 is Q2 = C1V2.

The charge transferred is:

$$\Delta Q = Q1 - Q2 = C1 \times (V1 - V2)$$

If the switch is cycled "F" times per second, the current (charge transfer per unit time) is:

$$I = F \times \Delta Q = F \times C1 \text{ (V1 - V2)}$$

Rearranging in terms of impedance:

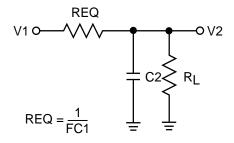

$$I = \frac{(V1-V2)}{(1/FC1)} = \frac{V1-V2}{REQ}$$

The 1/FC1 term can be modeled as an equivalent impedance REQ. A simple equivalent circuit is shown in figure 4. This circuit does not include the switch resistance nor does it include output voltage ripple. It does allow one to understand the switch-capacitor topology and make prudent engineering tradeoffs.

For example, power conversion efficiency is set by the output impedance, which consists of REQ and switch resistance. As switching frequency is decreased, REQ, the 1/FC1 term, will dominate the output impedance, causing higher voltage losses and decreased efficiency. As the frequency is increased quiescent current increases. At high frequency this current becomes significant and the power efficiency degrades.

The oscillator is designed to operate where voltage losses are a minimum. With external  $150\mu F$  capacitors, the internal switch resistances and the Equivalent Series Resistance (ESR) of the external capacitors determine the effective output impedance.

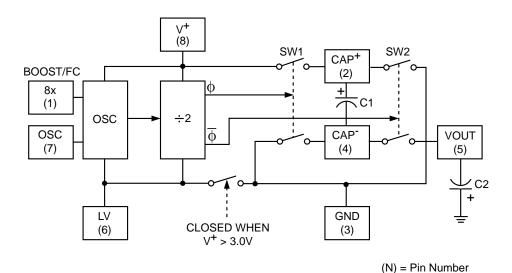

A block diagram of the CAT661 is shown in figure 5.

Figure 3. Switched-Capacitor Building Block

Figure 4. Switched-Capacitor Equivalent Circuit

#### OSCILLATOR FREQUENCY CONTROL

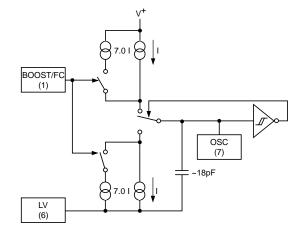

The switching frequency can be raised, lowered or driven from an external source. Figure 6 shows a functional diagram of the oscillator circuit.

The CAT661 oscillator has four control modes:

| BOOST/FC Pin Connection | OSC Pin Connection | Nominal Oscillator Frequency |  |

|-------------------------|--------------------|------------------------------|--|

| Open                    | Open               | 25kHz                        |  |

| BOOST/FC= V+            | Open               | 135kHz                       |  |

| Open or BOOST/FC= V+    | External Capacitor | _                            |  |

| Open                    | External Clock     | Frequency of external clock  |  |

If BOOST/FC and OSC are left floating (Open), the nominal oscillator frequency is 25kHz. The pump frequency is one-half the oscillator frequency.

By connecting the BOOST/FC pin to V+, the charge and discharge currents are increased, and the frequency is increased by approximately 6 times. Increasing the frequency will decrease the output impedance and ripple currents. This can be an advantage at high load currents. Increasing the frequency raises quiescent current but allows smaller capacitance values for C1 and C2.

If pin 7, OSC, is loaded with an external capacitor the frequency is lowered. By using the BOOST/FC pin and

an external capacitor at OSC, the operating frequency can be set.

Note that the frequency appearing at CAP+ or CAP- is one-half that of the oscillator.

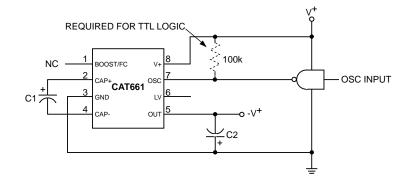

Driving the CAT661 from an external frequency source can be easily achieved by driving Pin 7 and leaving the BOOST pin open, as shown in figure 6. The output current from Pin 7 is small, typically 1 $\mu$ A to 8 $\mu$ A, so a CMOS can drive the OSC pin. For 5V applications, a TTL logic gate can be used if an external 100k $\Omega$  pull-up resistor is used as shown in figure 7.

Figure 5. CAT661 Block Diagram

# www.DataSheat4Lifton SELECTION

Low ESR capacitors are necessary to minimize voltage losses, especially at high load currents. The exact values of C1 and C2 are not critical but low ESR capacitors are necessary.

The ESR of capacitor C1, the pump capacitor, can have a pronounced effect on the output. C1 currents are approximately twice the output current and losses occur on both the charge and discharge cycle. The ESR effects are thus multiplied by four. A  $0.5\Omega$  ESR for C1 will have the same effect as a  $2\Omega$  increase in CAT661 output impedance.

Output voltage ripple is determined by the value of C2 and the load current. C2 is charged and discharged at a current roughly equal to the load current. The internal switching frequency is one-half the oscillator frequency.

VRIPPLE = IOUT/(FOSC x C2) + IOUT x ESRC2

For example, with a 25kHz oscillator frequency (12.5kHz switching frequency), a 150 $\mu$ F C2 capacitor with an ESR of 0.2 $\Omega$  and a 100mA load peak-to-peak the ripple voltage is 45mV.

**VRIPPLE vs. FOSC**

| VRIPPLE (mV) | IOUT (mA) | FOSC (kHz) | <b>C2 (μF)</b> | C2 ESR (Ω) |

|--------------|-----------|------------|----------------|------------|

| 45           | 100       | 25         | 150            | 0.2        |

| 25           | 100       | 135        | 150            | 0.2        |

Figure 6. Oscillator

Figure 7. External Clocking

## CAPACITOR SUPPLIERS

The following manufacturers supply low-ESR capacitors:

| Manufacturer   | Capacitor Type | Phone        | WEB                 | Email              | Comments |

|----------------|----------------|--------------|---------------------|--------------------|----------|

| AVX/Kyocera    | TPS/TPS3       | 843-448-9411 | www.avxcorp.com     | avx@avxcorp.com    | Tantalum |

| Vishay/Sprague | 595            | 402-563-6866 | www.vishay.com      | _                  | Aluminum |

| Sanyo          | MV-AX, UGX     | 619-661-6835 | www.sanyo.com       | Svcsales@sanyo.com | Aluminum |

| Nichicon       | F55            | 847-843-7500 | www.nichicon-us.com | _                  | Tantalum |

| -              | HC/HD          |              |                     |                    | Aluminum |

Capacitor manufacturers continually introduce new series and offer different package styles. It is recommended

that before a design is finalized capacitor manufacturers should be surveyed for their latest product offerings.

#### **CONTROLLING LOSS IN CAT661 APPLICATIONS**

There are three primary sources of voltage loss:

1. Output resistance

VLOSS = ILOAD x ROUT, where ROUT is the CAT661 output resistance and ILOAD is the load current.

2. Charge pump (C1) capacitor ESR:

VLOSSC1  $\approx$  4 x ESRC1 x ILOAD, where ESRC1 is the ESR of capacitor C1.

3. Output or reservoir (C2) capacitor ESR:

$VLOSSC2 = ESRC2 \times ILOAD$ , where ESRC2 is the ESR of capacitor C2.

Increasing the value of C2 and/or decreasing its ESR will reduce noise and ripple.

The effective output impedance of a CAT661 circuit is approximately:

Rcircuit ≈ Rout 661 + (4 x ESRC1) + ESRC2

## **VOLTAGE INVERSION POSITIVE-TO-NEGATIVE**

The CAT661 easily provides a negative supply voltage from a positive supply in the system. Figure 8 shows a typical circuit. The LV pin may be left floating for positive input voltages at or above 3.3V.

#### TYPICAL APPLICATIONS

Figure 8: Voltage Inverter

www.DataSheet4U.com

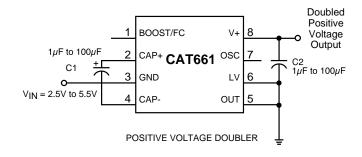

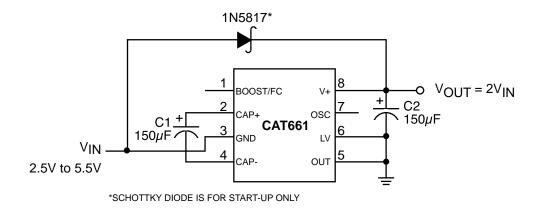

#### **POSITIVE VOLTAGE DOUBLER**

The voltage doubler circuit shown in figure 9 gives VOUT = 2 x VIN for input voltages from 2.5V to 5.5V.

Figure 9: Voltage Doubler

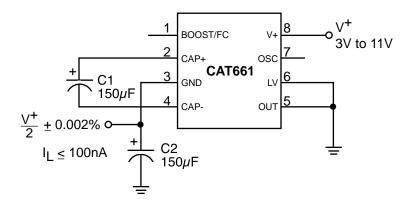

#### PRECISION VOLTAGE DIVIDER

A precision voltage divider is shown in figure 10. With load currents under 100nA, the voltage at pin 2 will be within 0.002% of V+/2.

Figure 10: Precision Voltage Divider (Load ≤ 100nA)

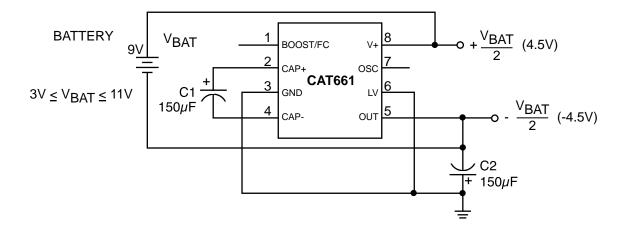

#### **BATTERY VOLTAGE SPLITTER**

Positive and negative voltages that track each other can be obtained from a battery. Figure 11 shows how a 9V battery can provide symmetrical positive and negative voltages equal to one-half the battery voltage.

Figure 11: Battery Splitter

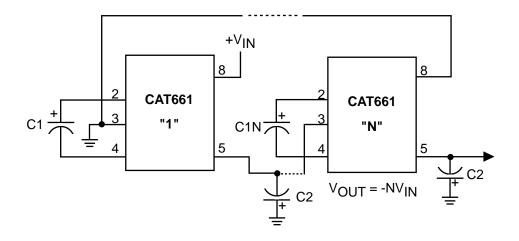

#### **CASCADE OPERATION FOR HIGHER NEGATIVE VOLTAGES**

The CAT661 can be cascaded as shown in figure 12 to generate more negative voltage levels. The output resistance is approximately the sum of the individual CAT661 output resistance.

V<sub>OUT</sub>= -N x V<sub>IN</sub>, where N represents the number of cascaded devices.

Figure 12: Cascading to Increase Output Voltage

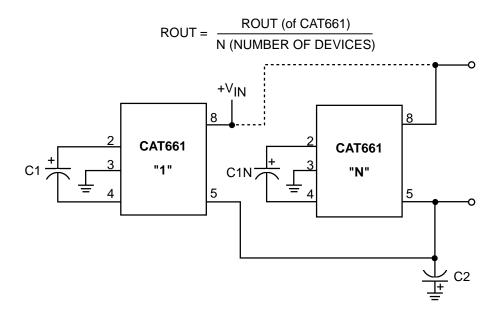

# www.DataSheet4U.com OPERATION

Paralleling CAT661 devices will lower output resistance. As shown in figure 13, each device requires its own pump capacitor, C2, but the output reservoir capacitor is shared with all devices. The value of C2 should be increased by a factor of N, where N is the number of devices.

Figure 13: Reduce Output Resistance by Paralleling Devices

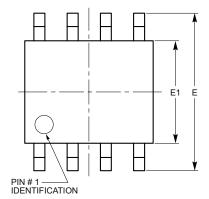

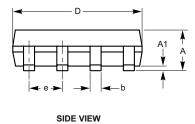

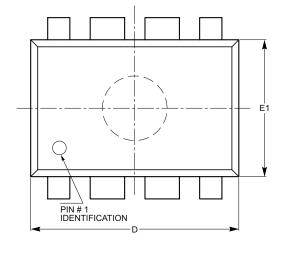

# PACKAGE OUTLINE DRAWINGS SOIC 8-Lead 150mils (V)

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| Α      | 1.35 |          | 1.75 |

| A1     | 0.10 |          | 0.25 |

| b      | 0.33 |          | 0.51 |

| С      | 0.19 |          | 0.25 |

| D      | 4.80 |          | 5.00 |

| E      | 5.80 |          | 6.20 |

| E1     | 3.80 |          | 4.00 |

| е      |      | 1.27 BSC |      |

| h      | 0.25 |          | 0.50 |

| L      | 0.40 |          | 1.27 |

| θ      | 0°   |          | 8°   |

**TOP VIEW**

**END VIEW**

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

#### Notes:

- 1. Al dimensions are in millimeters. Angles in degrees.

- 2. Complies with JEDEC standard MS-012.

www.DataSheet4U.com

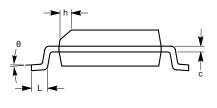

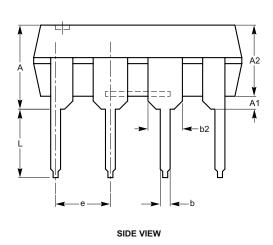

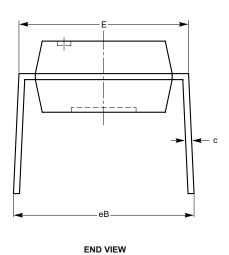

# PDIP 8-Lead 300mils (L)

| SYMBOL | MIN      | NOM  | MAX   |

|--------|----------|------|-------|

| Α      |          |      | 5.33  |

| A1     | 0.38     |      |       |

| A2     | 2.92     | 3.30 | 4.95  |

| b      | 0.36     | 0.46 | 0.56  |

| b2     | 1.14     | 1.52 | 1.78  |

| С      | 0.20     | 0.25 | 0.36  |

| D      | 9.02     | 9.27 | 10.16 |

| E      | 7.62     | 7.87 | 8.25  |

| е      | 2.54 BSC |      |       |

| E1     | 6.10     | 6.35 | 7.11  |

| eB     | 7.87     |      | 10.92 |

| L      | 2.92     | 3.30 | 3.80  |

**TOP VIEW**

For current Tape and Reel information, download the PDF file from: http://www.catsemi.com/documents/tapeandreel.pdf.

#### Notes

- 1. Al dimensions are in millimeters. Angles in degrees.

- 2. Complies with JEDEC standard MS-001.

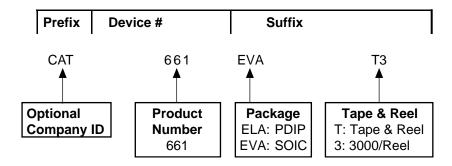

# \*\*\*\*\* EXAMPLE OF ORDERING INFORMATION

#### Notes

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard lead finish is Matte-Tin.

- (3) The device used in the above example is a CAT661W-T3 (SOIC, Tape & Reel).

# www.Datashatillon HISTORY

| Date       | Rev. | Reason                                                            |

|------------|------|-------------------------------------------------------------------|

| 10/15/03   | G    | Updated Description - eliminated Commercial temperature range     |

| 10/27/04   | Н    | Minor changes throughout data sheet                               |

| 1/20/2005  | I    | Changed ordering information for CAT661EXA to CAT661EVA           |

|            |      | Changed ordering information for CAT661EXA-TE13 to CAT661EVA-TE13 |

| 04/22/2005 | J    | Removed Preliminary Information from data sheet header            |

| 11/16/2007 | K    | Update Features and Description                                   |

|            |      | Update Package Outline Drawings and remove TDFN                   |

|            |      | Add Example of Ordering Information                               |

|            |      | Add Ordering Part Number                                          |

|            |      | Add "MD-" to document number                                      |

#### Copyrights, Trademarks and Patents

© Catalyst Semiconductor, Inc.

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

Adaptive Analog™, Beyond Memory™, DPP™, EZDim™, LDD™, MiniPot™, Quad-Mode™ and Quantum Charge Programmable™

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc. Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054 Phone: 408.542.1000

Fax: 408.542.1200 www.catsemi.com

www.DataSheet4U.com

MD-5003

11/16/07

Publication #:

Revison:

Issue date: